中国科学院官网刊文称,上海光机所在计算光刻技术研究方面取得重要进展。

近日,中科院上海光学精密机械研究所信息光学与光电技术实验室提出一种基于虚拟边(Virtual Edge)与双采样率像素化掩模图形(Mask pixelation with two-phase sampling)的快速光学邻近效应修正技术(Optical proximity correction, OPC)。仿真结果表明,该技术具有较高的修正效率。

光刻是极大规模集成电路制造的关键技术之一,光刻分辨率决定集成电路的特征尺寸。随着集成电路图形的特征尺寸不断减小,光刻系统的衍射受限属性导致明显的光学邻近效应,降低了光刻成像质量。

在光刻机软硬件不变的情况下,采用数学模型和软件算法对照明模式、掩模图形与工艺参数等进行优化,可有效提高光刻分辨率、增大工艺窗口,此类技术即计算光刻技术(Computational Lithography),被认为是推动集成电路芯片按照摩尔定律继续发展的新动力。

OPC技术通过调整掩模图形的透过率分布修正光学邻近效应,从而提高成像质量。基于模型的OPC技术是实现90nm及以下技术节点集成电路制造的关键计算光刻技术之一。

上海光机所科研人员提出的这种基于虚拟边、双采样率像素化掩模图形的快速光学邻近效应修正技术,能够将不同类型的成像失真归结为两种类型的成像异常,即内缩异常与外扩异常。

利用不同的成像异常检测模板,依次在掩模图形的边缘和拐角等轮廓偏移判断位置进行局部成像异常检测,确定异常类型及异常区域的范围。

根据异常检测位置与异常区域范围,自适应产生虚拟边。通过移动虚拟边调整掩模的局部透过率分布,从而修正局部成像异常。借助修正策略和修正约束,实现高效的局部修正和全局轮廓保真度控制。

另外,双采样率像素化掩模充分利用了成像系统的衍射受限属性,在粗采样网格上进行成像计算与异常检测,在精采样网格上进行掩模修正,兼顾了成像计算效率与掩模修正分辨率。

利用多种掩模图形进行验证,仿真结果表明该OPC技术的修正效率优于常用的基于启发式算法的OPC技术。

全球观察:端午节期间日均132.1万人次出入境 较去年增长约2.3倍 据国家移民管理局25日消息,2023年端午节期间全国边检机关共查验出入境

全球观察:端午节期间日均132.1万人次出入境 较去年增长约2.3倍 据国家移民管理局25日消息,2023年端午节期间全国边检机关共查验出入境

汽车博主发表贬损极狐汽车言论 极狐要求永久删除 近日,北汽极狐公司针对知名汽车博主袁启聪在抖音和微博发布的涉及极狐

汽车博主发表贬损极狐汽车言论 极狐要求永久删除 近日,北汽极狐公司针对知名汽车博主袁启聪在抖音和微博发布的涉及极狐  天天视点!极限 极限有高有低……心理极限极高的人可能身体会先到极限而出问题。身体极

天天视点!极限 极限有高有低……心理极限极高的人可能身体会先到极限而出问题。身体极  世界热推荐:观众齐喊“开空调”!梁静茹沈阳演唱会遭遇尴尬一幕 近期高温预警,再加上演出现场人员爆满,昨天是满场,估计昨天观看演唱

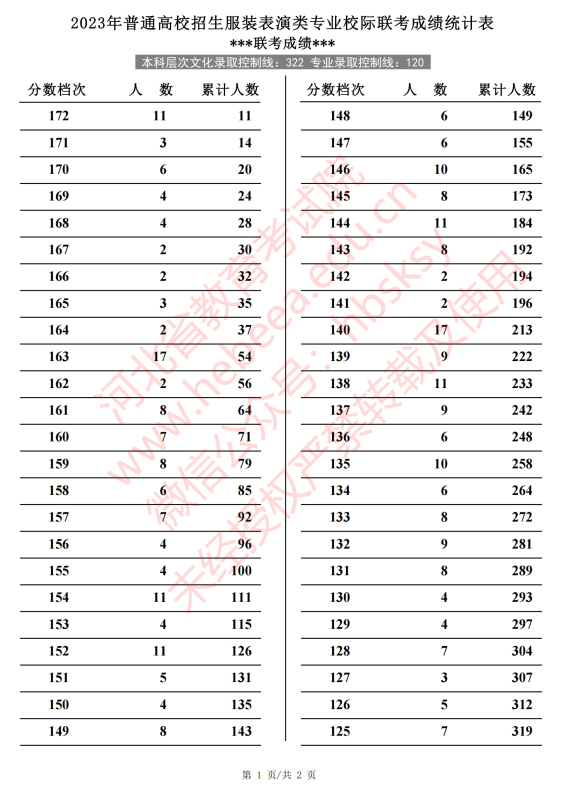

世界热推荐:观众齐喊“开空调”!梁静茹沈阳演唱会遭遇尴尬一幕 近期高温预警,再加上演出现场人员爆满,昨天是满场,估计昨天观看演唱  每日快看:2023年河北省普通高校招生服装表演类专业校际联考成绩统计表(专业成绩·综合成绩) 最新高考资讯、高考政策、考前准备、志愿填报、录取分数线等高考时间线

每日快看:2023年河北省普通高校招生服装表演类专业校际联考成绩统计表(专业成绩·综合成绩) 最新高考资讯、高考政策、考前准备、志愿填报、录取分数线等高考时间线  海口江东新区将建香港玉玲珑珠宝产业园 近日,记者从海口江东新区管理局获悉,位于海口江东新区离岸创新创业组

海口江东新区将建香港玉玲珑珠宝产业园 近日,记者从海口江东新区管理局获悉,位于海口江东新区离岸创新创业组